- 您现在的位置:买卖IC网 > Sheet目录1905 > ATMEGA8HVA-4CKU (Atmel)MCU AVR 8K FLASH 4MHZ 36-LGA

110

8024A–AVR–04/08

ATmega8HVA/16HVA

19.7.3

CADICH and CADICL - CC-ADC Instantaneous Current

When a CC-ADC Instantaneous Current conversion is complete, the result is found in these two

registers. CADIC[15:0] represents the converted result in 2's complement format. CADIC[12:0]

are the 13-bit ADC result (including sign), while CADIC[15:13] are the sign extension bits.

When CADICL is read, the CC-ADC Instantaneous Current register is not updated until CADCH

is read. Reading the registers in the sequence CADICL, CADICH will ensure that consistent val-

ues are read. When a conversion is completed, both registers must be read before the next

conversion is completed, otherwise data will be lost.

19.7.4

CADAC3, CADADC2, CADAC1, CADAC0 - CC-ADC Accumulate Current

The CADAC3, CADAC2, CADAC1 and CADAC0 Registers contain the Accumulate Current

measurements in 2's complement format. CADAC[17:0] are the 18-bit ADC result (including

sign), while CADAC[31:18] are the sign extension bits.

When CADAC0 is read, the CC-ADC Accumulate Current register is not updated until CADAC3

is read. Reading the registers in the sequence CADAC0, CADAC1, CADAC2, CADAC3 will

ensure that consistent values are read. When a conversion is completed, all four registers must

be read before the next conversion is completed, otherwise data will be lost.

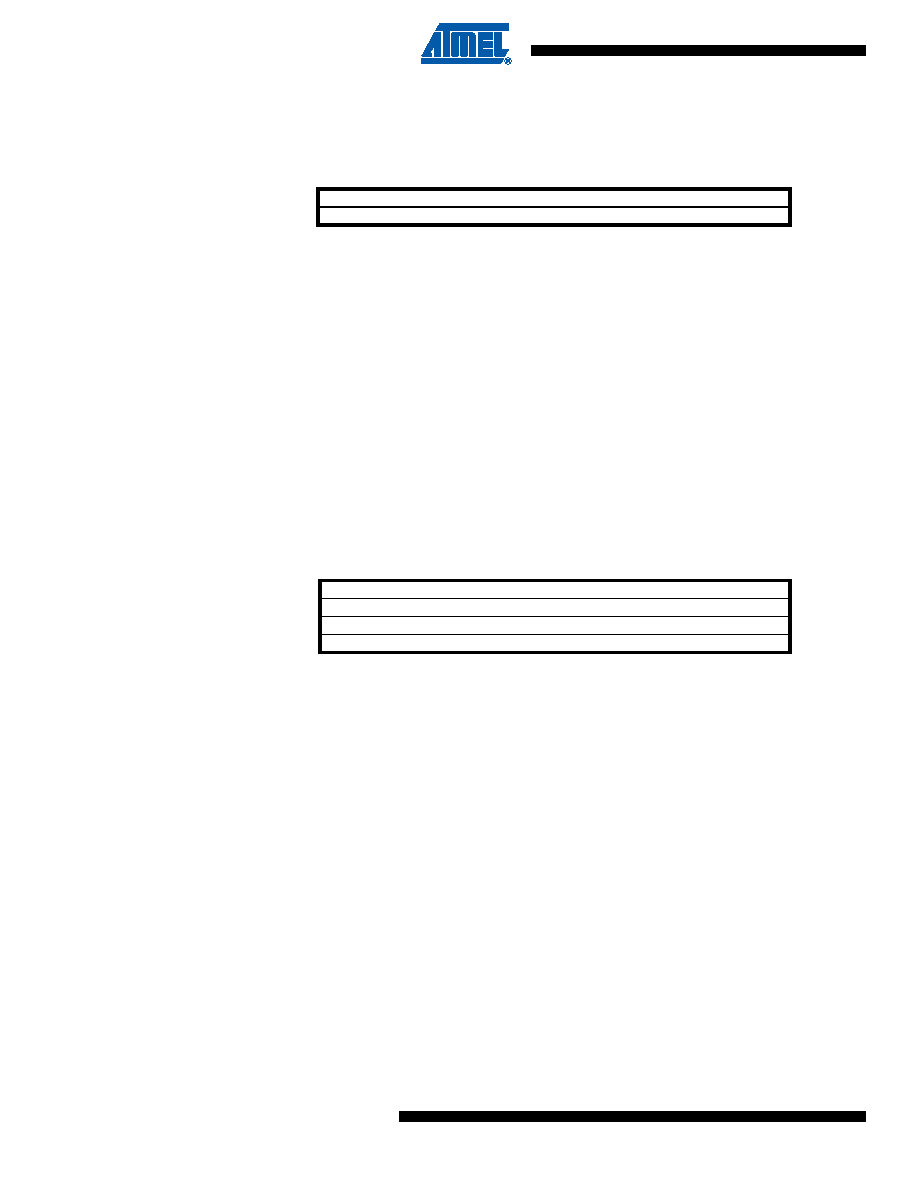

Bit

15141312

1110

9

8

765

43

210

CADIC[15:8]

CADICH

CADIC[7:0]

CADICL

Read/Write

R

RRR

RR

R

RRR

RR

Initial Value

0

000

00

000

Bit

313029

2827

262524

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6543210

CADAC[31:24]

CADAC3

CADAC[23:16]

CADAC2

CADAC[15:8]

CADAC1

CADAC[7:0]

CADAC0

Read/Write

RRRRR

RRR

RRRRR

RRR

RRRRR

RRR

Initial Value

0

0000000

0

0000000

0

0000000

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ATSAM3N4AA-AU

MCU FLASH 48-QFP

ATSAM3SD8CA-CU

IC MCU 2X256KB CORTEX-M3 100-QFN

ATSAM3U1EB-CU

IC MCU 64KB CORTEX-M3 144-TFBGA

ATSAM3X8EA-CU

IC MCU 2X256KB CORTEX-M3 144-BGA

ATTINY12V-1SUR

IC AVR MCU 1K FLASH 4MHZ 8-SOIC

ATTINY13-20SQR

IC MCU AVR 1KB FLASH 20MHZ 8SOIC

ATTINY13A-MMUR

MCU AVR 1KB FLASH 20MHZ 10DFN

ATTINY13V-10SUR

MCU AVR 1KB FLASH 10MHZ 8SOIC

相关代理商/技术参数

ATMEGA8HVA-4CKUR

功能描述:8位微控制器 -MCU AVR 8KB FLSH 512B EE 1KB SRAM - 4 MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8HVA-4TU

功能描述:8位微控制器 -MCU AVR 8KB, 512B EE 4MHz 1KB SRAM 1.8-9V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8HVA-4TUR

功能描述:8位微控制器 -MCU AVR 8KB FLSH 512B EE 1KB SRAM - 4 MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8HVD-4MX

功能描述:8位微控制器 -MCU AVR 8KB, 512B EE 4MHz 1KB SRAM 2.1-8V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8L-8AC

功能描述:8位微控制器 -MCU AVR 8K FLASH 512B EE 1K SRAM ADC 3V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8L8AI

制造商:Atmel Corporation 功能描述:

ATMEGA8L-8AI

功能描述:8位微控制器 -MCU AVR 8K FLASH 512B EE 1K SRAM ADC 3V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8L-8AJ

功能描述:IC MCU AVR 8K 5V 8MHZ 32-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:AVR® ATmega 标准包装:9 系列:87C 核心处理器:8051 芯体尺寸:8-位 速度:40/20MHz 连通性:UART/USART 外围设备:POR,WDT 输入/输出数:32 程序存储器容量:32KB(32K x 8) 程序存储器类型:OTP EEPROM 大小:- RAM 容量:256 x 8 电压 - 电源 (Vcc/Vdd):4.5 V ~ 5.5 V 数据转换器:- 振荡器型:内部 工作温度:0°C ~ 70°C 封装/外壳:40-DIP(0.600",15.24mm) 包装:管件